Le projet interdisciplinaire LEOPAR (Low-Energy On-chip Pre-processing for Activity Recognition ) s’inscrit dans le concept du « Near Sensor Computing », qui vise à prétraiter les données au plus près des capteurs afin de limiter la quantité de données à transmettre ou le nombre de calculs dans le processeur principal.

Le projet LEOPAR vise à explorer des structures de circuits innovantes, dans les technologies fortement intégrées, qui tirent parti des avantages du traitement des signaux analogiques et numériques pour optimiser la configurabilité, la consommation d’énergie et l’occupation du silicium de l’unité de prétraitement.

Circuits ultra-faible consommation pour la détection de signaux audio

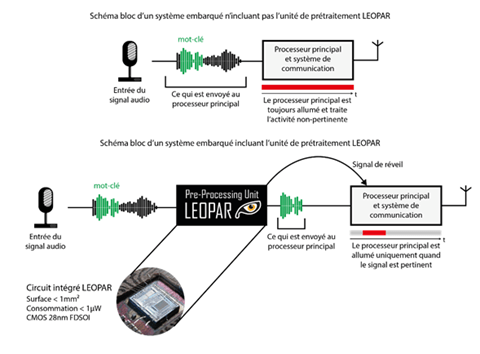

Le concept du « Near Sensor Computing » est un moyen courant de réaliser des économies d’énergie au niveau des nœuds consiste à mettre le processeur principal en veille la plupart du temps et à utiliser un signal de « réveil » pour indiquer l’activité et la pertinence du signal d’entrée. Le système générant le signal de « réveil » est donc actif tout le temps mais est généralement composé d’une fonction spécifique consommant très peu d’énergie. Par conséquent, la consommation totale d’énergie du système est réduite de plusieurs décades par rapport à un fonctionnement en continu. Le rôle de préprocesseur est donc double : il doit d’abord extraire des caractéristiques du signal d’entrée, puis en faire la classification pour déterminer leur pertinence. Par exemple, dans le domaine audio, des applications telles que la détection d’activité vocale dans un contexte bruyant, ainsi que des applications plus élaborées telles que les voyelles, les mots et la reconnaissance du langage, peuvent être ciblées.

Le projet LEOPAR vise à explorer des structures de circuits innovantes, dans les technologies fortement intégrées (Complementary Metal-Oxide-Seminconductor, CMOS), qui tirent parti des avantages du traitement des signaux analogiques et numériques pour optimiser la configurabilité, la consommation d’énergie et l’occupation du silicium de l’unité de prétraitement.

En ce qui concerne l’extraction de caractéristiques, le projet vise à étudier la possibilité d’utiliser le calcul numérique événementiel non conventionnel à temps continu.

Pour la classification, le projet explore la possibilité d’utiliser des mémoires associatives intégrées, qui se sont avérées efficaces dans le contexte ciblé du « Near Sensor Computing ». En outre, l’intégration efficace en énergie de modèles de classifieurs comme les « Long Short-Term Memories » sera également étudiée au cours du projet.

L’objectif final du projet est la conception et la fabrication d’un démonstrateur complet intégrant ces deux concepts, à haut rendement énergétique, et comprenant un prototype de circuit intégré dédié (Application-Specific Integrated Circuit, ASIC) de pré-traitement en technologie CMOS avancée.

- PI Benoit Larras benoit.larras@junia.com

- ANR AAPG Call 2018 – Jeunes Chercheurs – Jeunes Chercheuses

- Start date: December 2018

- Project total cost: 609 000€ / Funding support: 304 000€